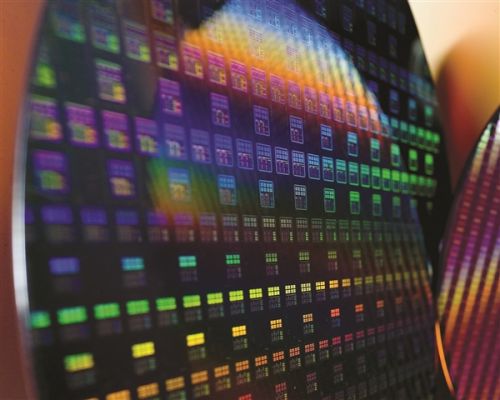

2.公司概况.PDF,2.公司概況2.1公司簡介台積公司成立於民國七十六年二月二十一日,總 的 CoWoS-XL技術已於民國一百零四年成功開發並台積公司提供客戶專業積體電路製造

四大主流的高级封装标准介绍

558x309 - 32KB - JPEG

里昂看好台积电CoWoS技术开发上调目标价 -

300x300 - 14KB - JPEG

Altera采用台积电CoWoS工艺实现异质混合3D

400x608 - 39KB - JPEG

Xilinx与TSMC宣布采用CoWoS(TM)技术全线量

480x384 - 197KB - JPEG

TSV技术持续突破 3D IC成本效益显著提升--华

650x241 - 77KB - JPEG

Xilinx与TSMC宣布采用CoWoS(TM)技术全线量

480x338 - 134KB - JPEG

特尔、AMD分别在ISSCC角力最新技术发展;环

623x473 - 34KB - JPEG

台积电提出堆叠晶圆技术:AMD\/NVIDIA显卡有望

500x400 - 31KB - JPEG

CTIMES - 瞄准台积电InFO技术 明导以两大平台

300x225 - 29KB - JPEG

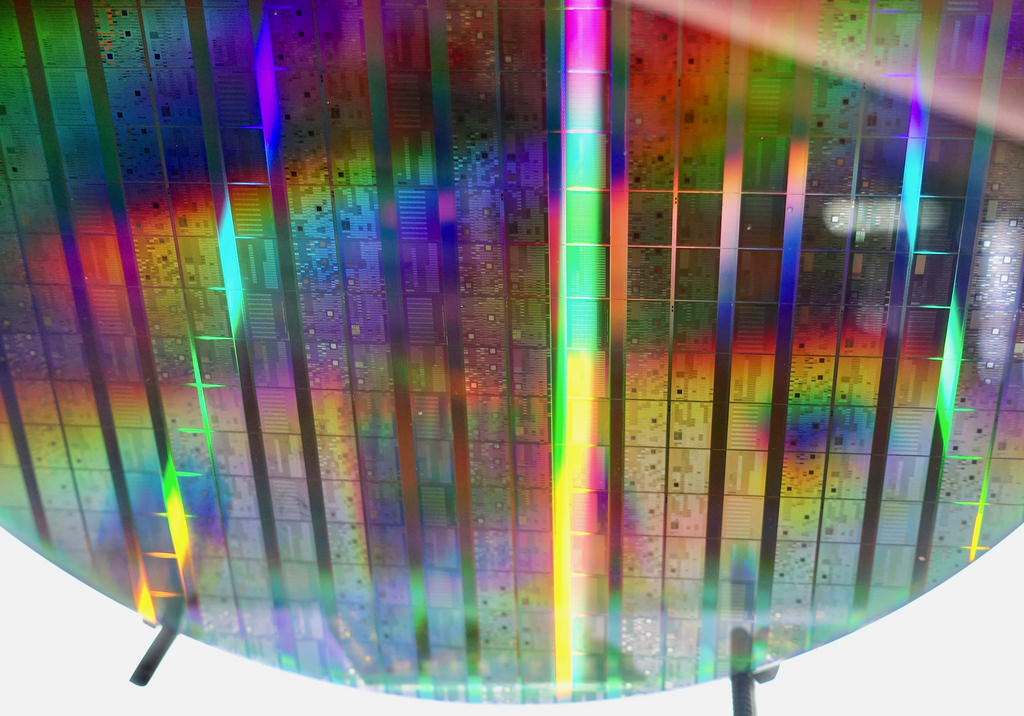

台积电宣布WoW堆叠晶圆技术,有望成倍提高核

1024x716 - 179KB - JPEG

AI概念起飞 2.5D\/3D IC封装技术迈进有望-AET

362x220 - 120KB - PNG

Technical Article

500x268 - 20KB - JPEG

台积电最新技术蓝图:5nm工艺明年试产 2nm以

640x424 - 38KB - JPEG

17:芯片领域的奥林匹克运动会-AET-电子技术应

510x234 - 23KB - JPEG

工智能芯片角逐千亿美元市场 - EDN电子技术设

633x353 - 51KB - JPEG