说明: verilog实现的流水线CPU通过仿真和下载验证 (verilog achieve pipelined CPU verified by simulation and downloads) lab28-他人 lab28-他人\ISE lab28-他人\ISE\DataRAM

Verilog课程设计.docx

794x1123 - 39KB - PNG

简化的RISC_CPU设计题库.doc

794x1123 - 75KB - PNG

简易CPU课程设计3.doc

141x200 - 3KB - PNG

Verilog:单周期CPU设计-程序设计-就爱阅读网

557x650 - 62KB - PNG

微程序控制型简单CPU模型Verilog HDL实现_

802x466 - 64KB - JPEG

verilog实现的16位CPU单周期设计 - 赫尔修罗

825x323 - 16KB - PNG

微程序控制型简单CPU模型Verilog HDL实现_

2686x1405 - 221KB - JPEG

Verilog:单周期CPU设计 - 综合编程类其他综合

571x440 - 85KB - PNG

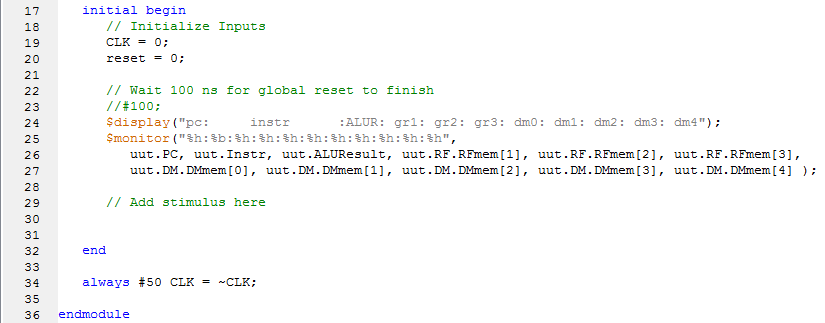

verilog实现16位五级流水线的CPU带Hazard冲

456x384 - 17KB - PNG

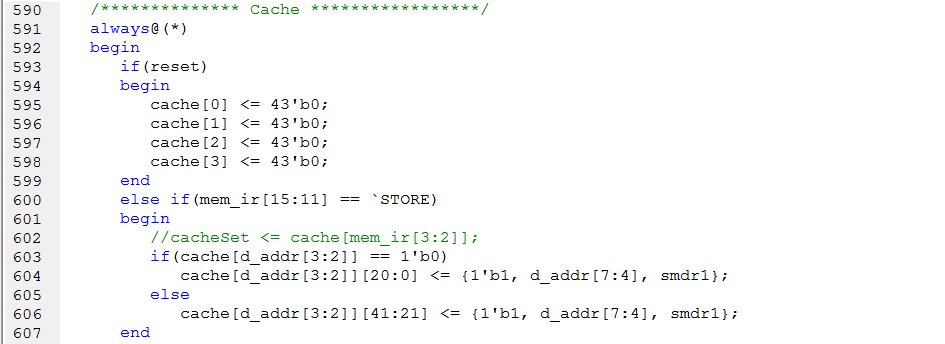

verilog简易实现CPU的Cache设计 - 赫尔修罗

945x344 - 22KB - PNG

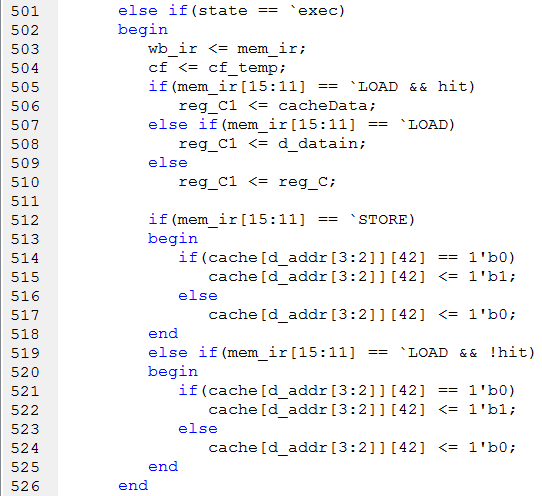

verilog简易实现CPU的Cache设计 - 赫尔修罗

542x496 - 27KB - PNG

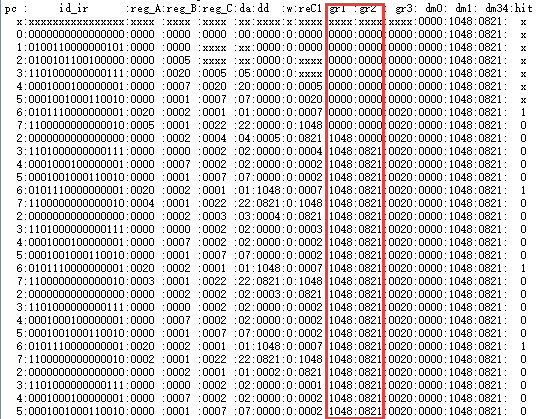

verilog简易实现CPU的Cache设计 - 赫尔修罗

538x419 - 28KB - PNG

SoC原型验证技术的研究

314x290 - 9KB - GIF

基于Verilog的实用CPU创新设计

1077x808 - 38KB - JPEG

第十讲 SystemVerilog写CPU_综合_测试_时序

448x252 - 19KB - JPEG