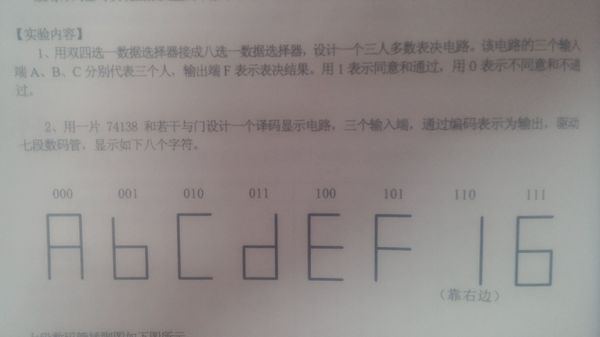

实验目标 1)熟悉译码器、数据选择器等中规模数字集成电路(MSI)的逻辑功能及其使用方法。 2)掌握用中规模集成电路构成组合逻辑电路的设计方法。 3)了解数字可编程逻辑器

计算机硬件技术基础实验6-中规模集成电路的应

993x1404 - 60KB - PNG

数电实验4-中规模集成电路功能测试及应用

893x1876 - 32KB - PNG

数电实验4-中规模集成电路功能测试及应用

620x251 - 17KB - JPEG

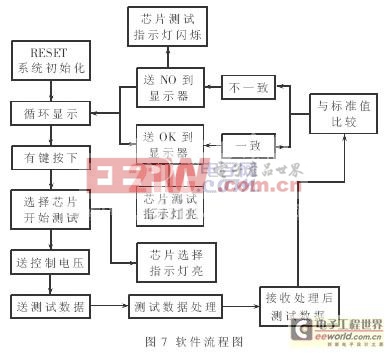

默认中规模集成电路功能测试仪的设计方案

388x353 - 64KB - PNG

数字逻辑实验 中规模集成组合逻辑电路的应用

600x337 - 13KB - JPEG

中规模集成电路功能测试仪的设计方案

388x353 - 59KB - JPEG

实验2 中规模集成电路实现组合逻辑

1080x810 - 45KB - JPEG

用中规模集成电路连接一个3位十进制数字显示

510x335 - 52KB - JPEG

中规模集成电路功能测试仪的设计方案

388x353 - 56KB - JPEG

中规模集成电路计数器的应用

474x355 - 15KB - GIF

实验二 中规模组合逻辑电路的设计.docx

794x1123 - 43KB - PNG

实验6.3中规模集成逻辑器件的应用解读.ppt

960x720 - 54KB - JPEG

(青岛大学)数字电路实验课件3 (计数器 时序逻辑

1080x810 - 83KB - JPEG

中规模集成电路功能测试仪的设计 测控论文 自

388x353 - 20KB - GIF

.jpg)

中规模集成电路功能测试仪的设计

388x353 - 43KB - JPEG