掌握cadence编辑环境,设计静态CMOS与非门逻辑电路原理图。3、掌握cadence仿真环境,完成反相器的仿真。三、与非门版图的设计方法1、确定工艺规则。2、绘制与非门版

版图设计必备!新扫描★CMOS电路设计.布局与

982x1470 - 483KB - PNG

大学毕业设计论文-cmos运算放大器版图设计.d

737x1021 - 25KB - PNG

CMOS运算放大器版图设计稿毕业设计稿.doc

141x200 - 7KB - PNG

论文CMOS运算放大器版图设计.doc

141x200 - 8KB - PNG

基于Cadence电路版图绘制和验证.ppt

1152x864 - 929KB - PNG

基于CMOS工艺的新型集成运算放大器设计

402x294 - 47KB - JPEG

CMOS射频集成电路设计实验.pdf

800x600 - 41KB - PNG

CMOS制作基本工艺解读.doc免费全文阅读

993x1404 - 95KB - PNG

基于Cadence电路(版本)图绘制和验证.ppt

141x200 - 6KB - JPEG

二输入与非门版图实验报告

962x685 - 80KB - PNG

高增益高线性度CMOS偶次谐波混频器设计 - 微

563x425 - 103KB - JPEG

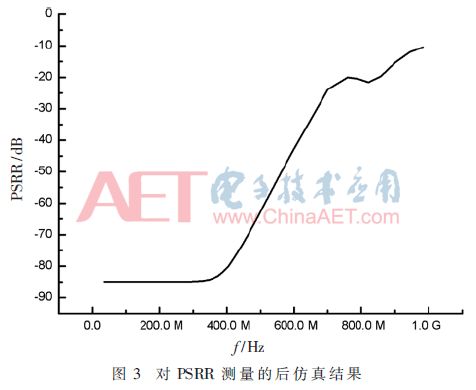

用于LED驱动器的改进型CMOS误差放大器的设

300x306 - 38KB - JPEG

一种用于高精度DAC的实用型CMOS带隙基准

476x390 - 16KB - JPEG

实验32 数字集成电路版图的反向提取.doc 3页

870x1229 - 94KB - PNG

![料 模拟技术] 用于LED驱动器的改进型CMOS误](http://www.ic37.com/2008file/tech/2010-5-10/20100510172304797_10434_5.jpg)

料 模拟技术] 用于LED驱动器的改进型CMOS误

299x305 - 87KB - JPEG