一些传统的单端和发射极耦合逻辑技术的局限性越来越明显。多点低电压差分信号(M-LVDS)是一种类似LVDS的接口标准,它可以为今天的总线应用带来高速、低功率和低EMI

(4)总线控制逻辑|mvb总线访问ip核逻辑框图

397x301 - 25KB - JPEG

(4)总线控制逻辑|逻辑大致分为reset 模块

655x356 - 50KB - JPEG

![[转载]I2C总线接口电路逻辑分析及功能简介(来](http://img.ddvip.com/2009_06_16/1245126503_ddvip_6617.jpeg)

[转载]I2C总线接口电路逻辑分析及功能简介(来

280x219 - 43KB - JPEG

(4)总线控制逻辑|逻辑大致分为reset 模块

436x278 - 15KB - JPEG

KL6904,TwinSAFE逻辑总线端子模块

604x520 - 38KB - JPEG

【逻辑IC总线收发器 SN74HC245N 全新原装 进

1024x768 - 303KB - JPEG

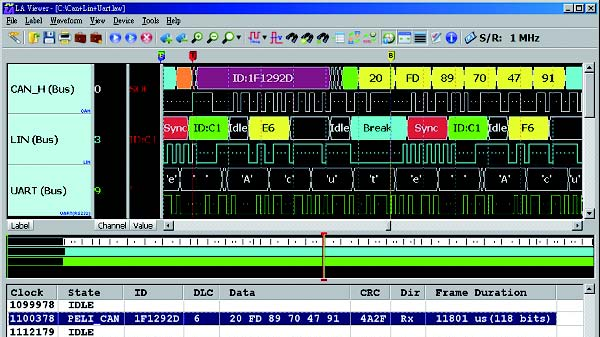

逻辑分析仪acute支持总线SPI

600x337 - 317KB - PNG

I2C总线接口逻辑分析

330x211 - 19KB - JPEG

74HC245D+NXP八路总线收发器逻辑

640x495 - 62KB - JPEG

总线控制逻辑的vhdl设计仿真与测试_产品创新

422x271 - 27KB - JPEG

SN74LVC125APWR 逻辑芯片 总线缓冲器 三态

500x375 - 31KB - JPEG

电子教材-多微处理器系统中总线仲裁逻辑的设

221x236 - 8KB - JPEG

【直插 HD74LS125AP 逻辑芯片 总线缓冲器 4

640x480 - 48KB - JPEG

Diodes推出多款八路逻辑器件 以简化数据总线

640x457 - 48KB - JPEG

总线控制逻辑的vhdl设计仿真与测试_产品创新

434x238 - 26KB - JPEG